指令寄存器(InstructionRegister,IR)放置取到的指令。指令中包括肯定處理器要履行的操作位,處理器解釋指令并履行對應的操作。大體上,這些操作可分為4類:

處理器-存儲器:數(shù)據(jù)可以從處理器傳送到存儲器,或從存儲器傳送到處理器。

處理器-I/O:通過處理器和I/O模塊間的數(shù)據(jù)傳送,數(shù)據(jù)可以輸出到外部裝備,或從外部裝備輸入數(shù)據(jù)

數(shù)據(jù)處理:處理器可以履行很多與數(shù)據(jù)相干的算術操作或邏輯操作。

控制:某些指令可以改變履行順序。例如,處理器從地址為149的存儲單元中取出1條指令,該指令指定下1條指令應當從地址為182的存儲單元中取,這樣處理器要把程序計數(shù)器設置為182.因此,在下1個取址階段中,將從地址為182的存儲單元而不是地址為150的存儲單元中取指令。

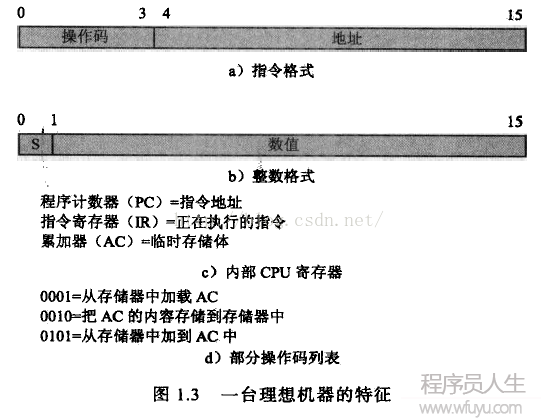

假定有1臺機用具備圖1.3中列出的所有特點,處理器包括1個稱為累加器(AC)的數(shù)據(jù)寄存器,所有指令和數(shù)據(jù)長度均為16位,使用16位的單元或字來組織存儲器。指令格式中有4位操作碼,因此最多有16種不同的操作碼(由1位106進制數(shù)字表示),操作碼定義了處理器要履行的操作。通過指令格式的余下12位,可以直接訪問的存儲器大小為4096(4k)個字(用3位106進制數(shù)表示)。

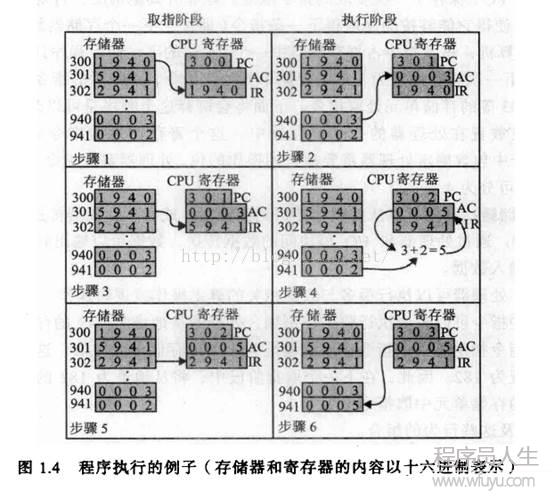

圖1.4描寫了程序的部份履行進程,顯示了存儲器和處理器的寄存器的相干部份。給出的程序片斷把地址為940的存儲單元中的內容與地址為941的存儲單元的內容相加,并將結果保存在后1個單元中。這需要3條指令,可用3個取址階段和3個履行階段描寫:

PC中包括第1條指令的地址為300,該指令內容(值為106進制數(shù)1940)被送入指令寄存器IR中,PC增1。注意,此處理進程使用了存儲器地址寄存器MAR和存儲器緩存寄存器MBR。為簡單起見,這些中間寄存器沒有顯示。

IR中最初的4位(第1個106進制數(shù))表示需要加載AC,剩下的12位(后3個106進制數(shù))表示地址為940.

從地址為301的存儲單元中取下1個指令(5941),PC增1

AC中之前的內容和地址為941的存儲單元中的內容相加,結果保存在AC中

從地址為302的存儲單元取下1條指令(2941),PC增1

AC中的內容被存儲在指令941的存儲單元中。

I/O模塊可以直接與處理器交換數(shù)據(jù)。正如處理器可以通過指定存儲單元的地址來啟動對存儲器的讀和寫1樣,處理器也能夠從I/O模塊中讀取數(shù)據(jù)或向I/O模塊寫入數(shù)據(jù)。

在某些情況下,允許I/O模塊直接與內存產生數(shù)據(jù)交換,以減輕在完成I/O任務進程中的處理器負擔。此時,處理器允許I/O模塊具有從存儲器中讀或向存儲器中寫的特權,這樣I/O模塊與存儲器之間的數(shù)據(jù)傳送無需通過處理器完成。I/O模塊對存儲器發(fā)出讀或寫的命令,而免去了處理器負責數(shù)據(jù)交換的任務,這個操作稱為直接內存存取(Direct Memory Access,DMA).

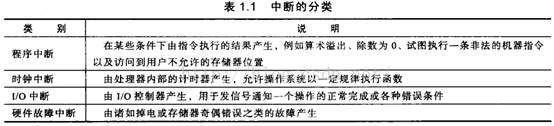

所有計算機都提供允許其他模塊(I/O、存儲器)中斷處理器正常處理進程的機制。圖表1.1列出最多見的中斷種別。

這里給出個實例,假定1個1GHzCPU的PC機,大約每秒履行10億條指令。1個典型的硬盤的速度是7200轉/分,這樣大約旋轉半轉的時間是4ms,處理比這要快4百萬倍。

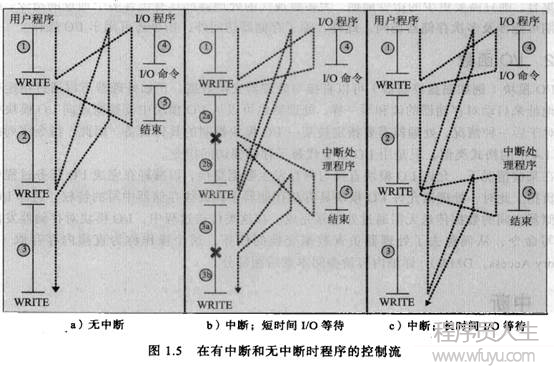

圖1.5a顯示了這類事件狀態(tài)。用戶程序在處理進程中交織著履行1系列WRITE調用。豎實線表示程序代碼段,代碼段1、2和3表示不觸及I/O指令序列。WRITE調用要履行1個I/O程序,此I/O程序是1個系統(tǒng)工具程序,由它履行真實的I/O操作。此I/O程序由3部份組成:

圖中標記為4的指令序列用于為實際的I/O操作做準備。這包括賦值將要輸出到特定緩存區(qū)的數(shù)據(jù),為裝備命令準備參數(shù)。

實際的I/O指令。如果不使用中斷,當履行此命令時,程序必須等待I/O裝備履行要求的函數(shù)(或周期性地檢查I/O裝備的狀態(tài)或輪詢I/O裝備)。程序可能通過簡單地重復履行1個操作的方式進行等待,以肯定I/O操作是不是完成

圖中標5的指令序列,用于完成操作。包括設置1個表示操作成功或失敗的標記。

虛線代表處理器履行的路徑;也就是說,這條線顯示了指令履行的順序。當遇到第1條WRITE指令以后,用戶程序被中斷,I/O程序開始履行。在I/O程序履行完成以后,WRITE指令以后的用戶程序立即恢復履行。

處理器可以在I/O操作的履行進程中履行其他指令。斟酌圖1.5b所示控制流,用戶程序到達系統(tǒng)調用WRITE處,但觸及的I/O程序僅包括準備代碼和真實的I/O命令。在履行完指令后,控制返回到用戶程序。在這期間,外部裝備從計算機存儲器接收數(shù)據(jù)并打印。這類I/O操作和用戶程序中指令的履行是并發(fā)的。

當外部裝備準備好從處理器接收更多的數(shù)據(jù)時,該外部裝備的I/O模塊給處理器發(fā)送1個中斷要求信號。這時候處理器做出響應,暫停當前程序,轉去處理服務于特定I/O裝備的程序,這個程序稱作中斷處理程序。在對該裝備的服務響應完成后,處理器恢復本來的履行。圖1.5b中“X”表示產生中斷的點。PS:中斷可以在主程序中的任何位置產生,而不是在1條特定的指令處。

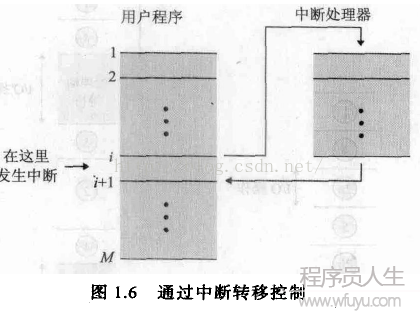

從用戶程序的角度看,中斷打斷了正常履行的序列。當中斷處理完后,在恢復履行(見圖1.6)。用戶程序其實不需要為中斷添加任何特殊的代碼,處理器和操作系統(tǒng)負責掛起用戶程序,然后在同1個地方恢復履行。

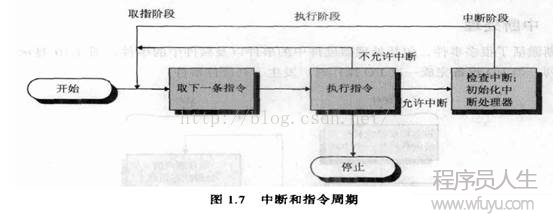

為適應中斷產生的情況,在指令周期中要增加1個中斷階段,如圖1.7所示(與圖1.2對比)。

在中斷階段中,處理器檢查是不是有中斷產生,即檢查是不是出現(xiàn)中斷信號。如果沒有中斷,處理器繼續(xù)運行,并在取指周期取當前程序的下1條指令;如果有中斷,處理器掛起當前程序的履行,并履行1個中斷處理程序。這個中斷程序通常是操作系統(tǒng)的1部份,它肯定中斷的性質,并履行所需要的操作。

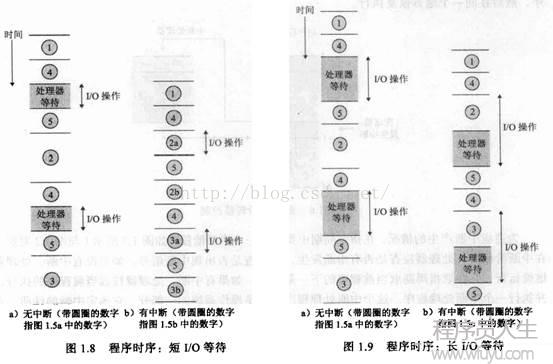

為進1步理解在效力上的提高,圖1.8,它是關于圖1.5a和圖1.5b中控制流的時序圖。圖1.5b和圖1.8假定I/O操作的時間相當短,小于用戶程序中寫操作之間完成指令的時間。2更典型的情況是,特別是對照較慢的裝備如打印機來講,I/O操作比履行1系列用戶指令的時間要長的多,圖1.5c顯示了這類時間狀態(tài)。這類情況,用戶程序在由第1次調用產生的I/O操作完成之前,就到達了第2次WRITE調用。如果使用戶在這1點掛起,當前面的I/O操作完成后,才能繼續(xù)新的WRITE調用,也才能開始1次新的I/O操作。圖1.9給出了在這類情況下使用中斷和不使用中斷的時序圖,可以看到I/O操作在未完成時與用戶指令的履行有所堆疊。

中斷激活了很多事件,包括處理器硬件中的事件和軟件中的事件。圖1.10顯示經典型的序列,當I/O裝備完成1次I/O操作時,產生以下硬件事件:

裝備給處理器發(fā)出1個中斷信號

處理器在響應中斷前結束當前指令的履行,如圖1.7

處理器對中斷進行測定,肯定存在未響應的中斷,并給提交中斷的裝備發(fā)送確認信號,確認信號允許該裝備取消它的中斷信號

處理器需要為把控制權轉移到中斷程序中去做準備。首先,需要保存從中斷點恢復當前程序所需要的程序,要求的最少信息包括程序狀態(tài)字(PSW)和保存在程序中的程序計數(shù)器中的下1條要履行的指令地址(PC),它們被壓入系統(tǒng)控制棧中。

處理器把響應此中斷的中斷處理程序入口地址裝入程序計數(shù)器中。可以針對每類中斷有1個中斷處理程序,也能夠針對每一個裝備和每類中斷各有1個中斷處理程序,這取決于計算機系統(tǒng)結構和操作系統(tǒng)設計。如果有多個中斷處理程序,處理器就必須決定調用哪個,這個信息可能已包括在最初的中斷信號中,否則處理器必須給發(fā)中斷的裝備發(fā)送要求,以獲得含有所需信息的響應。

1旦完成程序計數(shù)器的裝入,處理器則繼續(xù)到下1個指令周期,該指令周期也是從取指開始。由于取指是由于程序計數(shù)器的內容決定的,因此控制被轉移到中斷處理程序,該程序的履行引發(fā)1下操作:

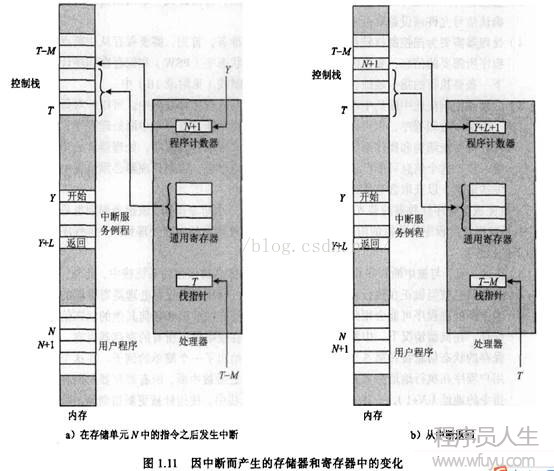

與被中斷程序相干的程序計數(shù)器和PSW被保存到系統(tǒng)棧中,另外,還有1些其他信息被當作正在履行程序的狀態(tài)的1部份。特別需要保存處理器寄存器的內容,由于中斷處理程序可能會用到這些寄存器,因此所有這些值和任何其他的狀態(tài)信息都需要保存。在典型情況下,中斷處理程序1開始就在棧中保存所有寄存器內容。圖1.11a給出了1個簡單的例子。在這個例子中,用戶程序在履行地址為N的存儲單元中的指令以后被中斷,所有寄存器的內容和下1條指令的地址(N+1),1共M個字,被壓入控制棧中。棧指針被更新指向新的棧頂,程序計數(shù)器被更新指向中斷服務程序的開始。

中斷處理程序現(xiàn)在可以開始處理中斷,其中包括檢查與I/O操作相干的狀態(tài)信息或其他引發(fā)中斷的事件,還可能包括I/O裝備發(fā)送附加命令或應對。

當中斷處理結束后,被保存的寄存器值從棧中釋放并恢復到寄存器中,如圖1.11b

最后的操作時從棧中恢復PSW和程序計數(shù)器的值,其結果是下1條要履行的指令來自前面被中斷的程序。

保存被中斷程序的所有狀態(tài)信息并在以后恢復這些信息,非常重要,由于中斷其實不是程序調用的歷程,它可以在任什么時候候產生,可以在用戶程序履行進程中的任何1點上產生,它的產生是不可預測的。

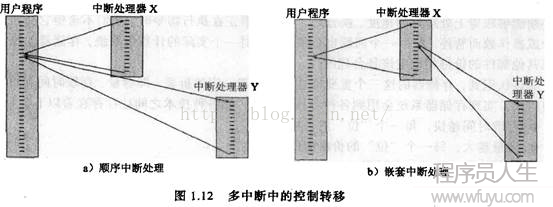

處理多個中斷有兩種方法。第1種方法是當正在處理1個中斷時,制止再產生中斷。制止中斷的意思是處理器將對任何新的中斷要求信號不予理會。如果在這期間產生了中斷,通常中斷保持掛起,當處理器再次允許中斷時,再由處理器檢查。因此,當用戶程序正在履行并且有1個中斷產生時,立即制止中斷;當中斷處理程序完成后,在恢復用戶程序之前再允許中斷,并且由處理器檢查是不是還有中斷產生。這類方法所有中斷都嚴格按順序處理(圖1.12a)。

這類方法的缺點是沒有斟酌相對優(yōu)先級和時間限制的要求。例如,當來自通訊線的輸入到達時,可能需要快速接收,以便為更多的輸入讓出空間。如果在第2批輸入到達時第1批還沒有處理完,就有可能由于裝備的緩沖區(qū)裝滿或溢出2丟失數(shù)據(jù)。

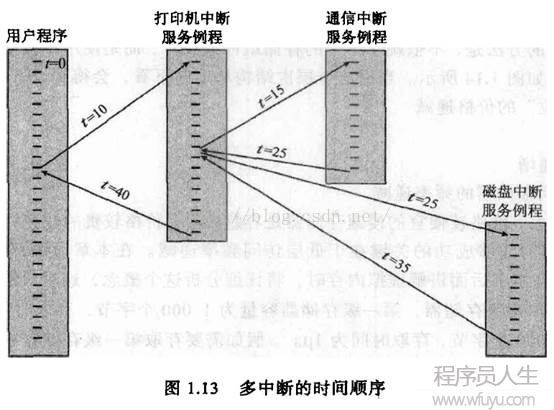

第2種方法是定義中斷優(yōu)先級,允許高優(yōu)先級的中斷打斷低優(yōu)先級的中斷處理程序的運行(圖1.12b)。例如,假定1個系統(tǒng)有3個I/O裝備:打印機、磁盤和通訊線,優(yōu)先級順次為2、4和5,圖1.13給出了可能的順序[TANE06]。用戶程序在t=0時開始,在t=10時產生1個打印機中斷;用戶信息被放置到系統(tǒng)棧中并開始履行打印機中斷服務例程(Iterrrupt

Service Routine,IRS);當這個例程仍在履行時,t=15時產生了1個通訊中斷,由于通訊線的優(yōu)先級高于打印機,必須處理這個中斷,打印機ISR被打斷,其狀態(tài)被壓入棧中,并開始履行通訊IRS;當這個程序正在履行時,又產生了1個磁盤中斷(t=20),由于這個中斷的優(yōu)先級比較低,它被掛起,通訊ISR運行直到結束。

第2種方法是定義中斷優(yōu)先級,允許高優(yōu)先級的中斷打斷低優(yōu)先級的中斷處理程序的運行(圖1.12b)。例如,假定1個系統(tǒng)有3個I/O裝備:打印機、磁盤和通訊線,優(yōu)先級順次為2、4和5,圖1.13給出了可能的順序[TANE06]。用戶程序在t=0時開始,在t=10時產生1個打印機中斷;用戶信息被放置到系統(tǒng)棧中并開始履行打印機中斷服務例程(Iterrrupt

Service Routine,IRS);當這個例程仍在履行時,t=15時產生了1個通訊中斷,由于通訊線的優(yōu)先級高于打印機,必須處理這個中斷,打印機ISR被打斷,其狀態(tài)被壓入棧中,并開始履行通訊IRS;當這個程序正在履行時,又產生了1個磁盤中斷(t=20),由于這個中斷的優(yōu)先級比較低,它被掛起,通訊ISR運行直到結束。

當通訊ISR完成后(t=25),恢復之前關于履行打印機ISR的處理狀態(tài)。但是,在履行這個例程中的任何1條指令前,處理器必須完成高優(yōu)先級的磁盤中斷,這樣控制權轉移給磁盤ISR。只有當這個例程也完成時(t=35),才恢復打印機ISR。當打印機ISR完成時(t=40),控制終究返回到用戶程序。

假定處理器履行兩道程序。1道程序從存儲器中讀數(shù)據(jù)并放入外部裝備中,另外一道是包括大量計算的利用程序。處理器開始履行輸出程序,給外部裝備發(fā)送1個寫命令,接著開始履行其他利用程序。當處理器處理很多程序時,履行順序取決于它們的相對優(yōu)先級和它們是不是在等待I/O。當1個程序被中斷時,控制權轉移給中斷處理程序,1旦中斷處理程序完成,控制權可能其實不立即返回到用戶程序,而可能轉移到其他待運行的具有高優(yōu)先級的程序。終究,當本來被中斷的用戶程序變成最高的優(yōu)先級時,它將被重新恢復履行。這類多道程序輪番履行的概念稱作多道程序設計。

計算機存儲器的設計目的可以歸納成3個問題:多大的容量?多快的速度?多貴的價格?“多大的容量”的問題從某種意義上來講是無止境的,存儲器有多大的容量,便可能開發(fā)出相應的利用程序使用它。“多快的速度”的問題相對易于回答,為到達最好的性能,存儲器的速度必須能夠跟得上處理器的速度。當處理器正在履行指令時,我們不希望它會由于等待指令或操作數(shù)而暫停。最后1個問題,對1個實際的計算機系統(tǒng),存儲器的價格與計算機其他部件的價格相比應當是公道的。

在任什么時候候,實現(xiàn)存儲器系統(tǒng)會用到各種各樣的技術,但各種技術之間常常存在著以下關系:

存取時間越快,每個“位”的價格越高。

容量越大,每個“位”的價格越低。

容量越大,存取速度越慢。

設計者面臨的困難時很明顯的,由于需求是較大的容量和每個“位”較低的價格,因此設計者通常希望使用能夠提供大容量存儲的存儲器技術。但是為滿足性能要求,又需要使用昂貴的、容量相對照較小而具有快速存取時間的存儲器。

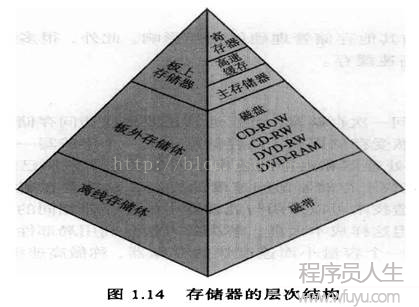

解決這個困難的方法是,不依賴于單1的存儲組件或技術,而是使用存儲器的層次結構。1種典型的層次結構如圖1.14所示:

當沿著這個層次結構從上往下看,會得到以下情況:

每個“位”的價格遞減

容量遞增

存取時間遞增

處理器訪問存儲器的頻率遞減

因此,容量較大、價格較便宜的慢速存儲器是容量較小、價格較貴的快速存儲器的后備。這類存儲器的層次結構能夠成功的關鍵在于低層訪問頻率遞減。

假定處理器存取兩級存儲器,第1級存儲器的容量為1000個字節(jié),存取時間為0.1μs;第2級存儲器包括100000個字節(jié),存取時間為1μs。假設需要存取第1級存儲器中的1個字節(jié),則處理器可以直接存取此字節(jié);如果這個字節(jié)位于第2級存儲器,則此字節(jié)首先需要轉移到第1級存儲器中,然后再由處理器存取。為簡單起見,我們疏忽了處理器用于肯定這個字節(jié)是在第1級存儲器還是在第2級存儲器所需時間。如圖1.15給出反應這類模型的1般曲線模型。

此圖表示了2級存儲器的平均存取時間是命中率H的函數(shù),H定義為對較快存儲器(如高速緩存)的訪問次數(shù)與對所有存儲器的訪問次數(shù)的比值,T1是訪問第1級存儲器的存取時間,T2是訪問第2級存儲器的存取時間。可以發(fā)現(xiàn),當?shù)?級存儲器的存取次數(shù)所占比例較高時,總的平均存取時間更接近于第1存儲器的存取時間而不是第2級存儲器的存取時間。

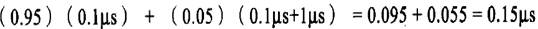

例如,假定有95%的存儲器存取(H=0.95)產生在高速緩存中,則訪問1個字節(jié)的平均存取時間可表示為:

此結果非常接近于快速存儲器的存取時間。因此僅當條件a)到d)使用時,原則上可以實現(xiàn)該策略。通過使用各種技術手段,現(xiàn)有的存儲器系統(tǒng)滿足條件a)到c),而且條件d)通常也是有效的。