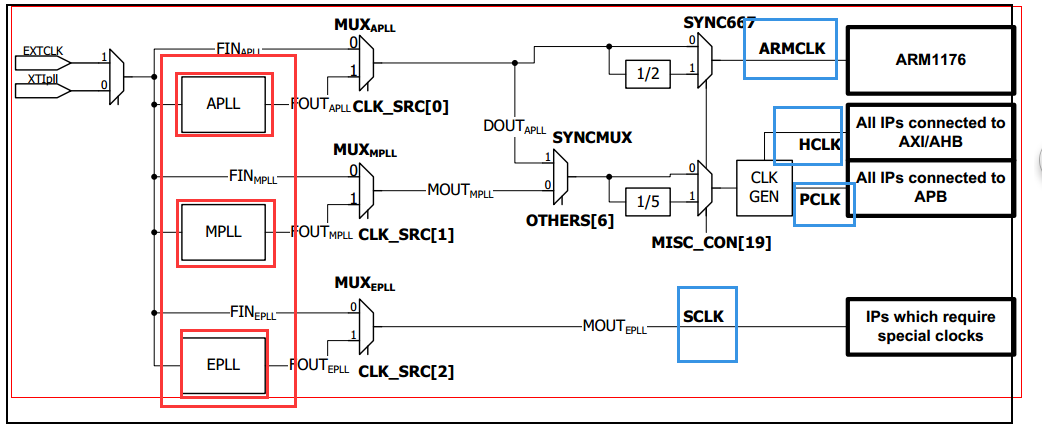

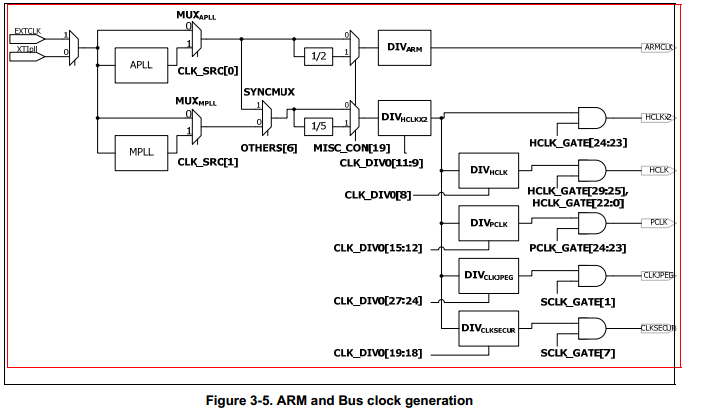

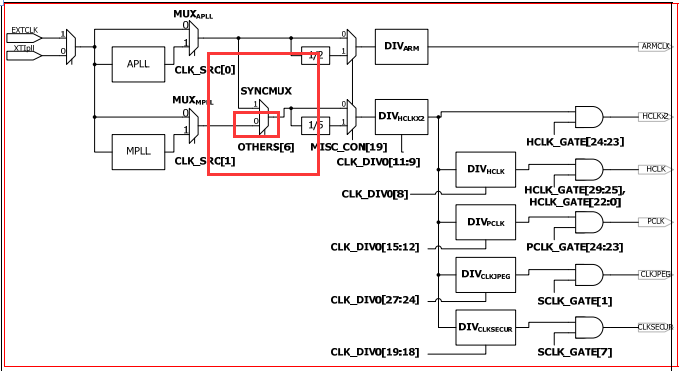

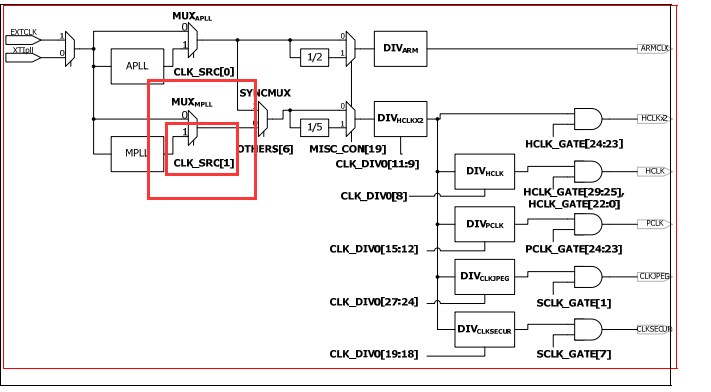

從上圖和原理圖可以知道下面的內(nèi)容:

1.采取12M的晶振

2 有3個(gè)分頻器 APLL MPLL EPLL

3.產(chǎn)生了4個(gè)時(shí)鐘 ACLK HCLK PCLK SCLK

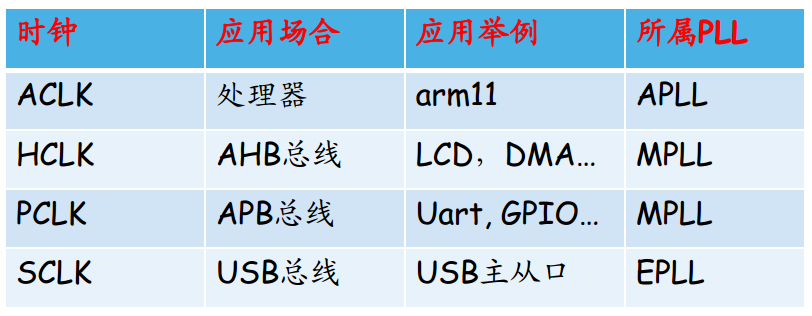

下面是幾個(gè)時(shí)鐘的利用范圍:

其中ACLK為系統(tǒng)時(shí)鐘,HCLK和PCLK為各種外設(shè)和內(nèi)部的時(shí)鐘,SCLK暫且不斟酌

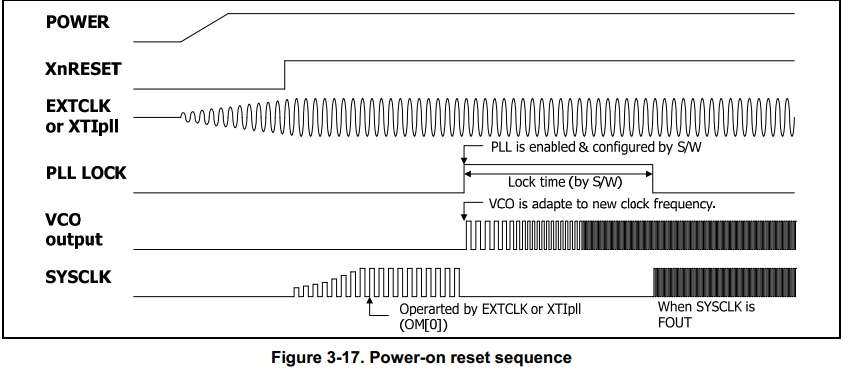

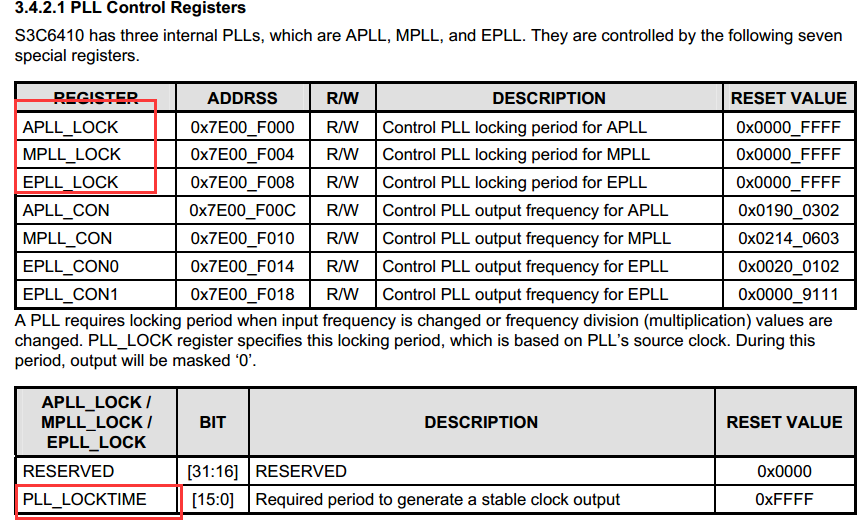

從上圖可以看出,SYSCLK為系統(tǒng)時(shí)鐘,起初頻率為12MHZ,當(dāng)設(shè)置頻率以后,系統(tǒng)頻率為有1段時(shí)間為0,這1時(shí)間為lock time ,如果要設(shè)置,可以對(duì)其進(jìn)行操作,但是,1般情況下不需要,保持默許便可.

設(shè)置時(shí)鐘,需要進(jìn)行1下幾個(gè)步驟:

1設(shè)置lock time

2.設(shè)置分頻系數(shù)

3.設(shè)置CPU到異步工作模式

4.設(shè)置APLL.MPLL輸出頻率

默許為初始值,所以不需要做

如上圖,6410共有3個(gè)locktime 分別為 APLL_LOCK MPLL_LOCK EPLL_LOCK,其寄存器的默許值都為0XFFFF,因此保持不變,不需要改變

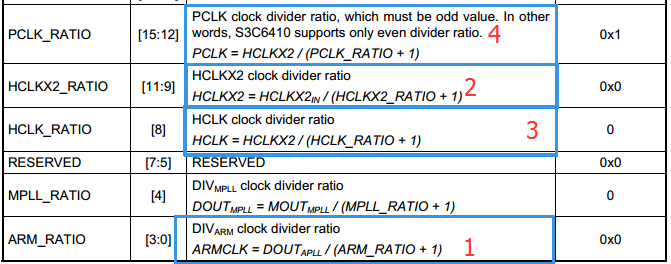

主要是設(shè)置 ACLK HCLK PCLK SCLK之間的比例關(guān)系或說(shuō)設(shè)置他們之間的頻率范圍

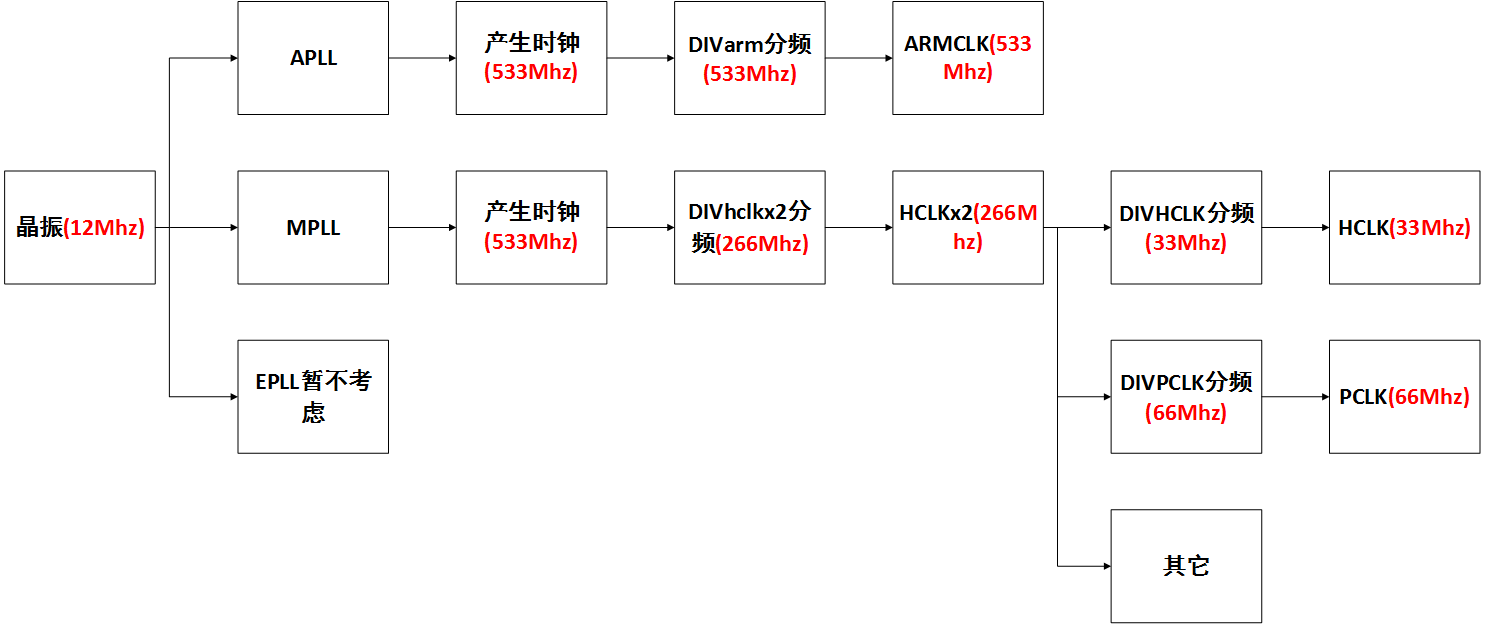

從上圖可以簡(jiǎn)化出頻率的產(chǎn)生進(jìn)程

其中紅色部份為本課時(shí)鐘需要的頻率,是根據(jù)uboot中6410的頻率得來(lái)的,因此需要根據(jù)設(shè)置好的頻率來(lái)設(shè)置參數(shù),

看上面兩幅圖,可以得知,要想設(shè)置ARMCLK HCLKX2 HCLK PCLK的頻率,需要設(shè)置

DIVarm DIVhclkx2 DIVhclk DIVpclk的值,

根據(jù)上圖的紅色編號(hào),可以肯定4個(gè)數(shù)的值

1.ARMCLK=533/(RATIO+1)=533 因此ARM_RATIO=0

即DIVarm=0

2.HCLKX2=533/(HCLKX2_RATIO+1)=266 因HCLKX2_RATIO=1

即DIVhclkx2=1

3.HCLK=HCLKX2/(HCLK_RATIO+1)=133 因此HCLK_RATIO=1

即DIVhclk=1

4.PCLK=HCLKX2/(PCLK_RATIO+1)=66 因此PCLK_RATIO=3

即DIVpclk=3

即:

#define CLK_DIV0 0x7e00f020

#define DIV_VAL ((0X0<<0)|(0X1<<9)|(0X1<<8)|(0X3<<12)) @

ldr r0,=CLK_DIV0 @設(shè)置分頻系數(shù)

ldr r1,=DIV_VAL @將DIV_VAL的值寫入寄存器

str r1,[r0]當(dāng)CPU工作時(shí)鐘和內(nèi)存的時(shí)鐘不1樣的時(shí)候,需要把CPU 的時(shí)鐘模式設(shè)為異步模式

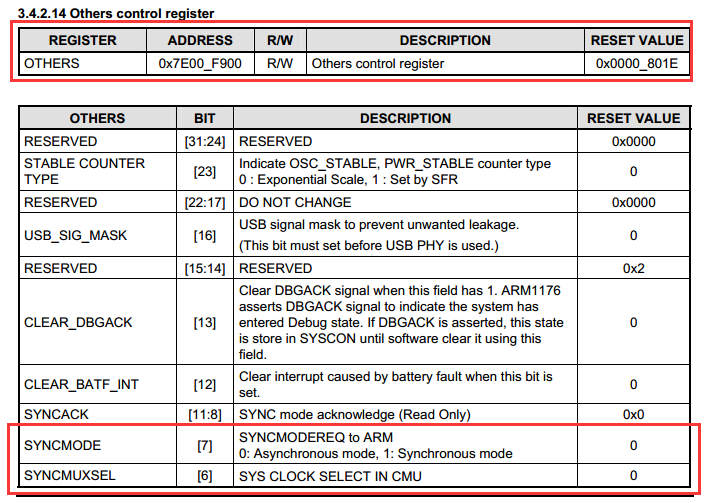

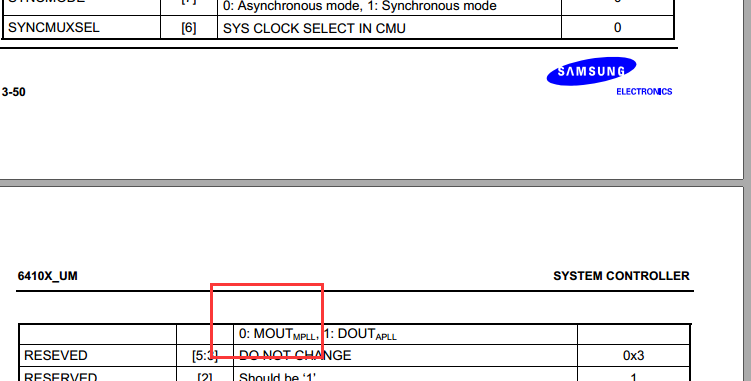

根據(jù)上圖,需要把第7位設(shè)置為0異步工作模式,同時(shí)也需要把第6位設(shè)置為0,主要緣由是使HCLKx2獲得到的時(shí)鐘源來(lái)自MPLL而不是APLL,以下圖所示。

#define OTHERS 0x7e00f900

ldr r0,=OTHERS @設(shè)置異步工作模式 第7位為0 第6位為0(時(shí)鐘選擇器)

ldr r1,[r0]

bic r1,r1,#0xc0 @

str r1,[r0]

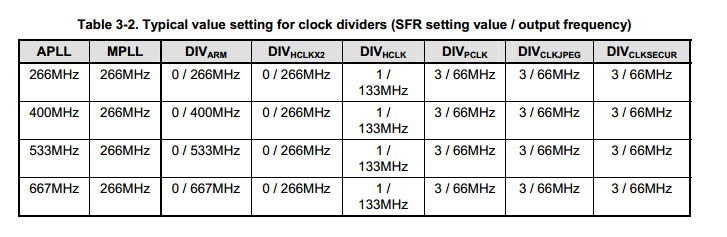

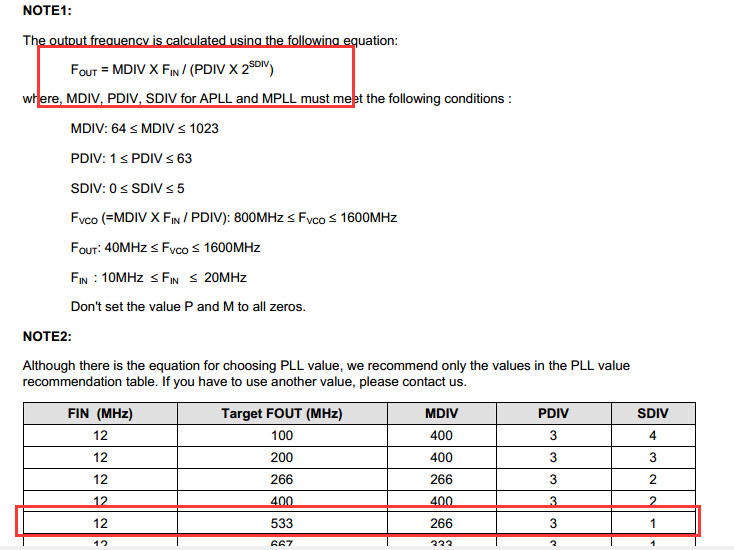

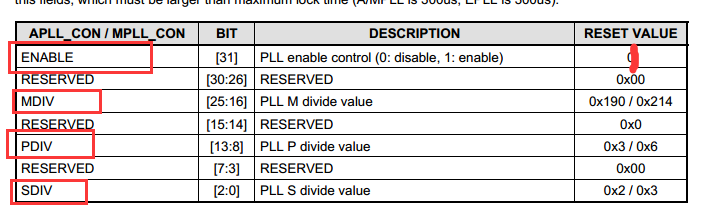

要想設(shè)置APLL和MPLL的值為533Mhz,根據(jù)上圖的計(jì)算公式和給出的表,可知需要設(shè)置 MDIV=266 PDIV=3 SDIV=1

根據(jù)下圖,則配置相應(yīng)的寄存器,同時(shí) 第31位 ENABLE位需要設(shè)置為1

#define MPLL_CON 0X7E00F010

#define APLL_CON 0X7E00F00c

#define PLL_VAL ((1<<31)|(266<<16)|(3<<8)|(1<<0))

ldr r0,=APLL_CON @設(shè)置為533Mhz

ldr r1,=PLL_VAL

str r1,[r0]

ldr r0,=MPLL_CON

ldr r1,=PLL_VAL

str r1,[r0]

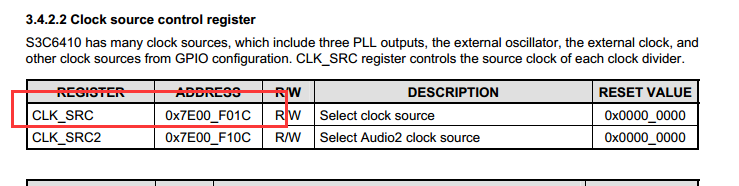

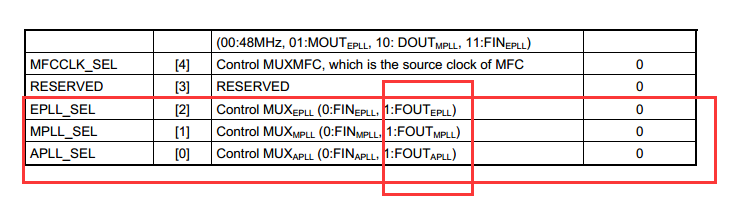

根據(jù)上圖,需要選擇使用是使用晶振頻率或MPLL作為后續(xù)時(shí)鐘源,因此需要設(shè)置CLK_SRC[1]=1

根據(jù)上面兩幅圖,將其寄存器配置為1

#define CLK_SRC 0x7e00f01c

ldr r0, =CLK_SRC @選擇時(shí)鐘源為APLL MPLL還是外部

mov r1, #0x3 @APLL MPLL

str r1, [r0]

mov pc,lr總的代碼:

@****************************

@name: start.S

@by : stone

@time: 2016.6.26

@function:

@ 異常向量表

@ 設(shè)置SVC模式

@ 關(guān)閉看門狗

@ 關(guān)閉中斷

@ 關(guān)閉MMU

@ 外設(shè)基地址初始化

@ 點(diǎn)亮LED

@ 時(shí)鐘初始化

@****************************

.text

.global _start @將_start聲明為全局變量

_start:

b reset

ldr pc, _undefined_instruction

ldr pc, _software_interrupt

ldr pc, _prefetch_abort

ldr pc, _data_abort

ldr pc, _not_used

ldr pc, _irq

ldr pc, _fiq

_undefined_instruction: .word undefined_instruction

_software_interrupt: .word software_interrupt

_prefetch_abort: .word prefetch_abort

_data_abort: .word data_abort

_not_used: .word not_used

_irq: .word irq

_fiq: .word fiq

undefined_instruction: @處理未定義指令異常

nop

software_interrupt: @軟中斷

nop

prefetch_abort: @預(yù)取指令異常

nop

data_abort: @數(shù)據(jù)訪問(wèn)異常

nop

not_used: @空位

nop

irq: @中斷

nop

fiq: @快速中斷

nop

reset: @reset

bl set_svc @設(shè)置為SVC模式

bl set_peri_port @外設(shè)基地址初始化

bl disable_watchdog @關(guān)閉看門狗

bl disable_interrupt @關(guān)閉中斷

bl disable_mmu @關(guān)閉mmu

bl init_clock @時(shí)鐘初始化

bl light_led @點(diǎn)亮LED

set_svc:

mrs r0, cpsr @將值取出cpsr寄存器

bic r0, r0, #0x1f @將后5位 即M[4:0]清零

orr r0, r0, #0xd3 @0b10011 轉(zhuǎn)化為16進(jìn)制為0x13 同時(shí)為了屏蔽irq和fiq,可以將其設(shè)置為0b11010011即0xd3

msr cpsr, r0 @將值送回cpsr寄存器

mov pc, lr @返回

set_peri_port:

ldr r0, =0x70000000 @基地址

orr r0, r0, #0x13 @256MB

mcr p15,0,r0,c15,c2,4 @寫入cp15

mov pc, lr

#define pwTCON 0x7E004000 @WTCON寄存器

disable_watchdog:

ldr r0, =pwTCON @把地址裝載到R0

mov r1, #0x0 @置0,關(guān)閉看門狗

str r1,[r0]

mov pc,lr

disable_interrupt:

mvn r1,#0x0 @0x0 取反,給r1

ldr r0,=0x71200014 @VIC0

str r1,[r0]

ldr r0,=0x71300014 @VIC1

str r1,[r0]

mov pc,lr

disable_mmu:

mcr p15,0,r0,c7,c7,0 @使ICACHE 和DCACHE 無(wú)效

mrc p15,0,r0,c1,c0,0 @read control register

bic r0,r0,#0x00000007 @mmu 和 dcache置零

mcr p15,0,r0,c1,c0,0 @write control register

mov pc,lr

#define CLK_DIV0 0x7e00f020

#define CLK_SRC 0x7e00f01c

#define OTHERS 0x7e00f900

#define MPLL_CON 0X7E00F010

#define APLL_CON 0X7E00F00c

#define PLL_VAL ((1<<31)|(266<<16)|(3<<8)|(1<<0))

#define DIV_VAL ((0X0<<0)|(0X1<<9)|(0X1<<8)|(0X3<<12))

init_clock:

ldr r0,=CLK_DIV0 @設(shè)置分頻系數(shù)

ldr r1,=DIV_VAL

str r1,[r0]

ldr r0,=OTHERS @設(shè)置異步工作模式 第7位為0 第6位為0(時(shí)鐘選擇器)

ldr r1,[r0]

bic r1,r1,#0xc0

str r1,[r0]

ldr r0,=APLL_CON @APLL設(shè)置為533Mhz

ldr r1,=PLL_VAL

str r1,[r0]

ldr r0,=MPLL_CON @MPLL設(shè)置為533Mhz

ldr r1,=PLL_VAL

str r1,[r0]

ldr r0, =CLK_SRC @選擇時(shí)鐘源為APLL MPLL還是外部

mov r1, #0x3 @APLL MPLL

str r1, [r0]

mov pc,lr

#define GPMCON 0x7F008820 @控制寄存器

#define GPMDAT 0x7F008824 @數(shù)據(jù)寄存器

light_led:

ldr r0,=GPMCON

ldr r1,=0x1111 @輸出模式

str r1,[r0]

ldr r0,=GPMDAT

ldr r1,=0x00 @低電平點(diǎn)亮

str r1,[r0]

mov pc,lr菜鳥(niǎo)1枚,如有毛病,多多指教。。。